# Micro-35 Tutorial Open Research Compiler (ORC) 2.0 and Tuning Performance on Itanium

#### **Presenters:**

Roy Ju, Sun Chan, Tin-Fook Ngai (MRL, Intel Labs) Chengyong Wu, Yunzhao Lu, Junchao Zhang (ICT, CAS)

Presented at the 35th International Symposium on Microarchitecture (Micro-35)

Istanbul, Turkey November 19, 2002

## Micro-35 Tutorial Open Research Compiler (ORC) 2.0 and Tuning Performance on Itanium

#### **Presenters:**

Roy Ju, Sun Chan, Tin-Fook Ngai (MRL, Intel Labs) Chengyong Wu, Yunzhao Lu, Junchao Zhang (ICT, CAS)

Presented at the 35th International Symposium on Microarchitecture (Micro-35)

Istanbul, Turkey November 19, 2002

intel,

ORC Tutorial

### Agenda

- Overview of ORC

- IR WHIRL and Optimizations

- Overview of CG

- Performance Features in ORC 2.0

- Performance Analysis Tools and Experience

- Demo

- ORC for Speculative Multithreading

- Research Activities and Plan

intطِ

#### **Overview of ORC**

intel。

ORC Tutorial

#### **ORC**

- <u>Objective</u>: provides a leading open source IPF (IA-64) compiler infrastructure to the compiler and architecture research community

- Requirements:

- Robustness

- → Timely availability

- **对** Flexibility

- Performance

intطِ

\* IPF for Itanium Processor Family in this presentation

#### What's in ORC?

- C/C++ and Fortran compilers targeting IPF

- Based on the *Pro64 (Open64)* open source compiler from SGI

- Retargeted from the MIPSpro product compiler

- → open64.sourceforge.net

- Major components:

- → Front-ends: C/C++ FE and F90 FE

- Interprocedural analysis and optimizations (IPA)

- ▼ Loop-nest optimizations (LNO)

- → Scalar global optimizations (WOPT)

- Code generation (CG)

- On Linux

intel.

### The ORC Project

- Initiated by Intel Microprocessor Research Labs (MRL)

- Joint efforts among

- Programming Systems Lab, MRL

- Institute of Computing Technology, Chinese Academy of Sciences

- 7 Intel China Research Center, MRL

- Core engineering team: 15 20 people

- Received support from the Open64 community and various users

intel.

7 ORC Tutorial

### The ORC Project (cont.)

- Development efforts started in Q4 2000

- ORC 1.0 released in Jan '02

- ORC 1.1 released in July '02

- Accomplishments:

- Zargely redesigned CG

- Enhanced IPA and WOPT

- Various enhancements to boost performance

- ▼ Tools and other functionality

- ORC 2.0 planned early '03

intطِ

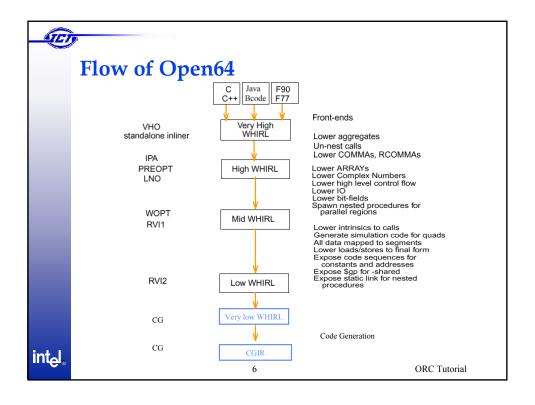

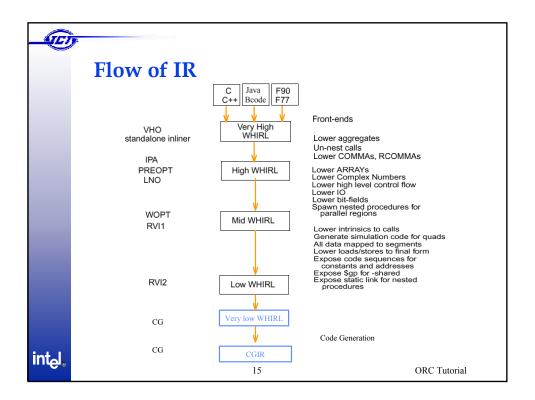

### IR - WHIRL and Optimizations

intel.

9

ORC Tutorial

### Role of IR in Compiler

- Bridge semantic gap from source language to machine instructions

- Same IR

- multiple languages

- multiple targets

- Interfaces between compiler components

10

- → Well defined input and output

- Medium for IR-based optimizations

intطِ

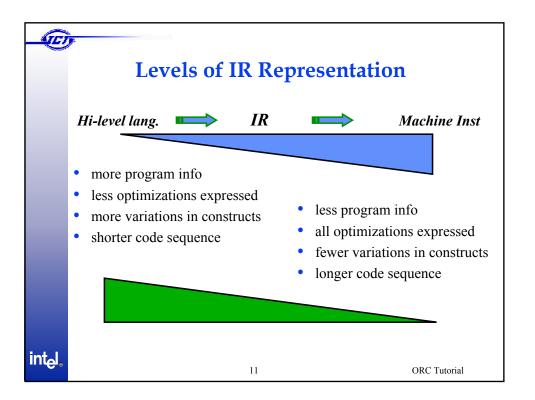

### Impact of IR on Optimizations

- Ease of implementation

- Info is right at hand

- Canonical form reduces implementation complexity

- Ease of debugging

- → Ability to verify consistency

- Well defined input/output

- Compile time efficiency

- No need for extra info to help analysis

- Quality of optimizations performed

- > Well formed IR prevents need to pattern match

- Canonical form improves chance to optimize

- Type of optimizations possible

- No lost of information when optimization done at the right level

12

intel,

#### **WHIRL**

- An Intermediate Representation of a given user program

- Multiple levels of abstraction

- **➣** Each level semantically the same

- Less information at lower level

- Allow optimization to be perform at most appropriate representation

- Hierarchical

- lower level subset of the higher form

- Symbol table

- User defined symbols

- User defined types

intel.

13 ORC Tutorial

#### **WHIRL**

- Continuous lowering of IR through each component

- → Call *lowerer* to translate to lower level

- Supporting components to

- → minimize variations in IR form

- Avoid duplication of optimization/analysis functionalities

Simplifier

Preopt

• High WHIRL and up can be raised back to C/Fortran

14

intطِ

#### **Tools for WHIRL**

- *ir\_b2a*

- → Dumps IR in pre/post order form

- whirl2c, whirl2f

- Dumps IR in high level C/Fortran form

- May not be re-compilable if input is low-WHIRL

- Numerous verifier and self-checkers throughout compiler

16

- WHIRL consistency

- → Symbol table and WHIRL consistency

intel,

#### **Tools for WHIRL**

• To get IR file after each component:

.N (after LNO or Preopt) -PHASE:c=off:w=off

.O (after Wopt) -PHASE:c=off

.B (after Frontend) -keep

.I (after IPA or Inlining) -keep

intel.

17

ORC Tutorial

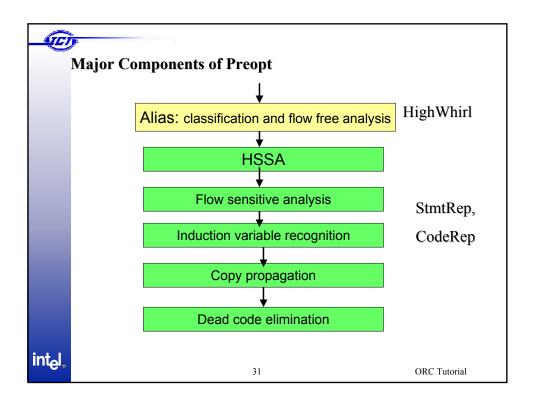

### **Normalization - PreOpt**

- Runs before *IPA*, *LNO*, *WOPT*

- Prepares and clean up code

- Expose more opportunities

- Minimize variations in IR forms

- Collect supporting info for later phases

- Alias info

- Loop info: trip count, body, induction expression,

. . .

• SSA slices for IPA summary info

18

intطا

### Simplification (Simplifier)

- Callable at anytime during compilation when WHIRL is the IR (i.e. before code generator)

- Works on expressions

- Constant folding

- Reassociation

- → Simple strength reduction

- Canonicalization

- Compiler writer is guaranteed a well formed expression for any expression he generates

intel,

9 ORC Tutorial

### **Optimization Topics Switch Case Optimization**

- Simple switch cases

- → Use cascaded if-then-else sequences

- Large switch cases with skewed frequent cases

- → Hoist most frequent cases outside of switch case

- IR Very High WHIRL *SWITCH, CASEGOTO*

- Implementation advantages

- → No need for control flow analysis

- No need to update control flow structure

20

intطِ

### **Optimization Topics Array Dependency Analysis**

- Dependency of subscripted variables inside loops

- Model as a system of integer programming

- Canonical form for indices to start at 1

- → Loops must be well form do loops (vs while, repeat)

- IR ARRAYEXP and DO\_LOOP

- High WHIRL

- Implementation advantages

- No need for do loop recognition in that component

- 7 Pointer access and array access produces same result

intel,

21 ORC Tutorial

### **Optimization Topics Data Flow Problems**

- Operate over program's control structure and flow of data

- → Simple model of program transfer points

- Uniform treatment of memory accesses

- IR Mid WHIRL

- Explicit control transfer

- → Full address expression form

$$X[I-1][J-1]$$

$\Rightarrow$  &X + (J-1) \* sizeof(X) - (I-1)

- Implementation advantages

- → Simpler algorithms for various control dependency data structure

- 7 No need to update loop structures after transformation

22

intel,

### **Optimization Topics Memory Disambiguation**

- Dependency of given pair of memory accesses

- Memory access variations

- Direct

- Explicitly indirect

- Pointer dereference

- Implicitly indirect

- Structure field access

- ABI requirement (access through global offset table)

- Indirect access manifests as:

&base + offset

intel,

3 ORC Tutorial

### **Optimization Topics Memory Disambiguation**

VH WHIRL *ldid v1*

Mid WHIRL ldid v1

Low WHIRL Machine Inst *lda &v1 adds r1=sp,16*

iload  $ld8 \quad r2=[r1]$

- Address taken detrimental to precision

- 7 Indirect access interfere with address taken analysis

- Reference parameter access after inlining

e.g.

$$\&p \rightarrow f$$

best if seen as  $p.f$

• Performed when IR is High WHIRL:

LDID object

where object is scalar, struct, field in struct, ...

- Implementation advantages

- More precise address taken analysis

- Overlaps in memory is exactly represented in same IR node

intel,

### **Optimization Topics Structure Field Reorder**

- Reorders layout of fields inside an aggregate object

- Effectively manipulates base address + offset

- Implementation considerations

- Base address and/or field offset in disguised form

- User code written as such

- Results of optimization (e.g. CSE of offset arithmetic)

- zizeof and offset operators in user code

in user code

- New order must be reflected consistently throughout user program

- Layout assumptions outside of current compilation unit

- Object preemption rules

intel,

25 ORC Tutorial

### **Optimization Topics Structure Field Reorder**

- IR Memory chunk type (M) in memory access

e.g. *MISTORE* indirect store of memory chunk

- Field ID provided in IR when access is expressed as individual field operation

- High WHIRL

- Symbol table contains *FLD\_TAB*

- → Byte offset, bit offset

- Other info such as equivalence to another object

26

intel,

### **Optimization Topics Structure Field Reorder**

- Implementation advantages

- No need to hunter for base address

- No need to distinguish between offset and constant in IR

- No restriction on type of optimizations done ahead

- Those optimizations must guarantee consistency though

- Not solved issues

- Need *sizeof* and *offset* operators

intel.

27 ORC Tutorial

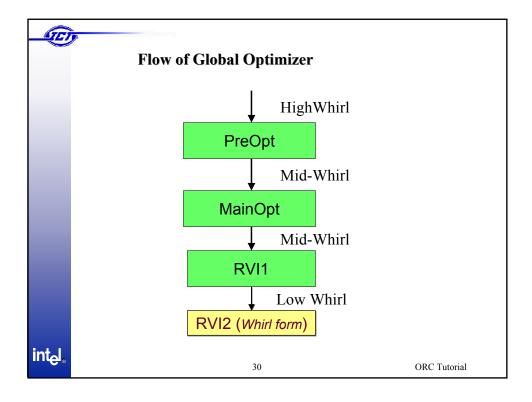

Major Flow of Global Optimizer

intel.

28

### IR inside Global Optimizer (Wopt)

- WHIRL is **NOT** an SSA language

- WHIRL is translated into HSSA form inside Wopt

- HSSA is a SSA form, extended to include

- Array and indirect memory references

- → Alias (mod/ref) info as part of the IR

- Representation in

- expression trees (*coderep*)

- Statements (*stmtrep*)

intطِ

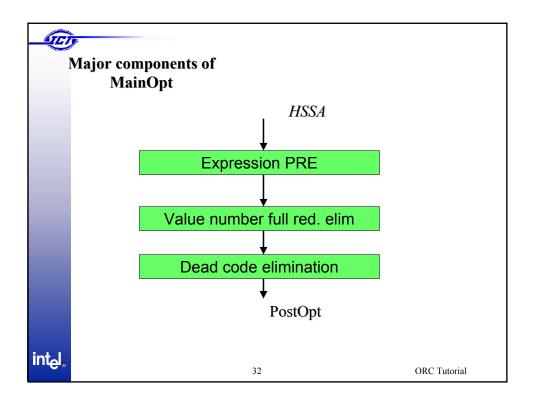

### **Detailed IR Lowering**

- Various specific lowering of expression occur during MainOpt

- 7 To take better advantage of optimization at hand

34

- → Extract/Deposit in replace of LDBITS

- → Signed-ness of load exposed

- **7 &***p*->*i* folded to *p*.*I*

- Redo address taken analysis

intel.

### Value Number Full Redundancy Elim.

- Some redundancy cannot be eliminated by PRE (and vice versa)

- Fast mechanism to deal with important cases where PRE misses

- Induction coalescing for some important loops

- Experimental phase to evaluate and explore new ideas (turned on by default)

intel.

ORC Tutorial

### **Partial Redundancy Elimination**

- Subsumes most major classical optimizations

- Common subexpression

- **▼** Loop invariant code motion

- → Strength reduction

- Code hoisting

- Redundancy elimination (partial and full)

- Register Promotion (Register variable identification)

- Partial dead store elimination

intel.

### SSA based PRE (SSAPRE)

- Result also in SSA form

- Advantage over bit vector approach

- Performs on local and global level in one shot

- Demand driven enable

- · Prioritized worklist

- Re-optimize previously optimized item for secondary effect

- → Sparse evaluation, demand driven plus result in SSA

- Optimization can stop at any work item

- **尽** Suitable for use in time sensitive environment (JIT)

- Enable automatic debug/triage tool for the compiler

- 7 Optimized code debugging becomes annotation problem

- Code motion done in one shot

- Almost linear time algorithm

intel.

37 ORC Tutorial

### Expression PRE (EPRE)

- Works on expression level

- Indirect memory operations are treated as other expressions

- → Covers indirect memory operations

- → Arbitrary tree size

- Arbitrary levels of indirects

- Easy to expand to other optimizations

- Array bounds check elimination

- → Speculative code motion

- **7** ...

ألطint

38

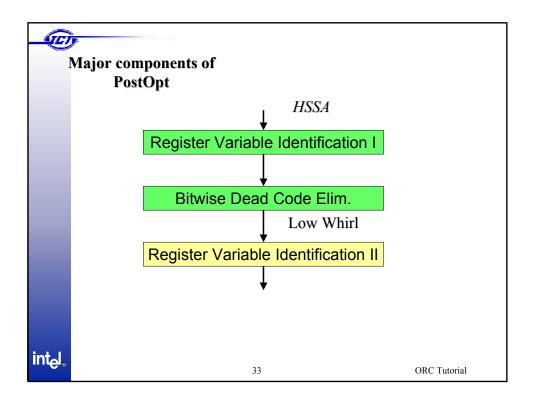

### Register Variable Identification (Register Promotion)

- Preparation phase for register allocation

- Problem formulated as PRE problem with lifetime optimal placement solution

- Advantage over non-PRE approach

- Placement not random, but provably lifetime optimal

- → Easily extensible to resource optimal also

- Advantage over non-SSA approach

- → Demand driven controllable compile time

- → Enable automatic debug/triage tool

intel.

39 ORC Tutorial

### Register Variable Identification (RVI)

- 3 separate phases of RVI I

- → Shares same code as EPRE for 2 phases

- Software reuse

- Zero Local register promotion

- Simple scan over all locals

- **↗** LPRE

- Works on loads of variables

- → SPRE

- Works on stores of variables

40

لطint

### **Register Variable Identification II**

- Works on Low-Whirl

- → Binary level details exposed

- bss segment, gp relative, ...

- → IR closer to machine form

- Load of variable value becomes

- Calculate address

- Load content through address

- Solves data flow equation over CFG

- Remnants of pre-SSAPRE implementation

- **对** Takers, any?

intel.

41

ORC Tutorial

### **Overview of CG**

42

intel.

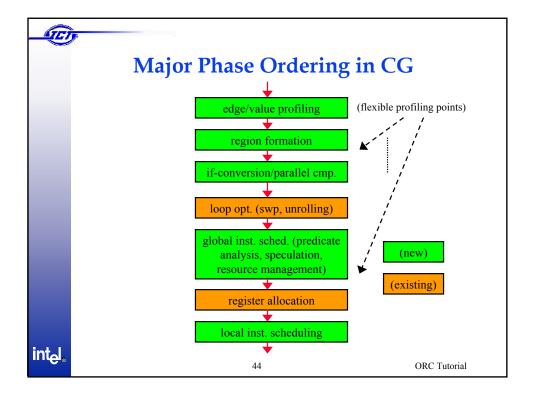

#### What's new in CG?

- CG has been largely redesigned from Open64

- Research infrastructure features:

- Region-based compilation

- Rich profiling support

- Parameterized machine descriptions

- IPF optimizations:

- If-conversion and predicate analysis

- Control and data speculation with recovery code generation

- Global instruction scheduling with resource management

- Other enhancements

intel,

### **Region-based Compilation**

- Motivations:

- 7 To form profitable scopes for optimizations

- 7 To control compilation time and space

- Region:

- A directed graph

- Connected subset of CFG

- Acyclic

- → Single-entry-multiple-exit

- More general than hyperblocks, treegion, etc

- Regions under hierarchical relations

- Regions could be nested within regions

intel,

5 ORC Tutorial

### Region-based Compilation (cont.)

- Region structure can be constructed and deleted at different optimization phases

- Optimization-guiding attributes at each region

- Region formation algorithm decoupled from the region structure

- → Algorithm posted on ORC web site

- Consider size, shape, topology, exit prob., code duplication, etc.

- Being used to support multi-threading research

46

intel,

### **Profiling Support**

- Edge profiling at WHIRL in Open64 remained and extended

- New profiling support added in CG to allow various instrumentation points

- Types of profiling:

- ▼ Edge profiling, value profiling, memory profiling, ...

- Important for limit study or collecting program statistics

- User model:

- Instrumentation and feedback annotation at the same compilation phase

- Zater phases maintain valid feedback information through propagation and verification

intel,

7 ORC Tutorial

#### **If-conversion**

- Converts control flow (branches eliminated) to predicated instructions

- A simple design to iteratively detect patterns for if-conversion candidates within regions

- Consider critical path length, resource usage, br mispred. rate & penalty, # of inst., etc.

- Utilizes parallel compare instructions to reduce control dependence height

- Invoked after *region formation* and before *loop optimization*

- Displaces the hyperblock formation in Open64

intel,

### **Predicate Analysis**

- Analyze relations among predicates and control flow

- Relations stored in Predicate Relation Database (PRDB)

- Query interface to PRDB: disjoint, subset/superset, complementary, sum, difference, probability, ...

- PRDB can be deleted and recomputed as wish without affecting correctness

- No coupling between the if-conversion and predicate analysis

- Currently used during the construction of dependence DAG for scheduling

- Can be used for predicate-aware data flow analysis

intel.

49 ORC Tutorial

### **Global Instruction Scheduling**

- Performs on the scope of SEME regions

- Cycle scheduling with priority function based on frequencyweighted path lengths

- Full resource management by interacting with a microscheduler

- Modularizes the legality and profitability checking

50

- Includes

- → Safe speculation across basic blocks

- Control and data speculation

- Code motion with compensation code

- Partial ready code motion

- Motion of predicated instructions

- 7

أبطint

### **Control and Data Speculation**

- Features missing in Open64 but added in ORC

- Speculative dependence edges added on DAG

- Selection of speculation candidates driven by scheduling priority function

- For a speculated load, insert *chk* and add DAG edges to ensure recoverability

- Recovery code generation decoupled from scheduling phase

- Starting from the speculative load, follow flow and output dependences to re-identify speculated instructions

- GRA to properly color registers in recovery blocks

intel.

1 ORC Tutorial

#### **Parameterized Machine Model**

- Motivations:

- 7 To centralize the architectural and micro-architectural details in a well-interfaced module

- 7 To facilitate the study of hardware/compiler co-design by changing machine parameters

- 7 To ease the porting of ORC to future generations of IPF

- Read in the (micro-)architecture parameters from KAPI (Knobsfile API) published by Intel

- Automatically generate the machine description tables in Open64

52

• Being ported to Itanium 2

intطِ

#### Micro-Scheduler

- Manages resource constraints

- ▶ E.g. templates, dispersal rules, FU's, machine width, ...

- Models instruction dispersal rules

- Interacts with the high-level instruction scheduler

- Reorders instructions within a cycle

- Uses a finite state automata (FSA) to model the resource constraints

- → Each state represents occupied FU's

- State transition triggered by incoming scheduling candidate

- Can be ported to other tools as a standalone phase

intel。

53 ORC Tutorial

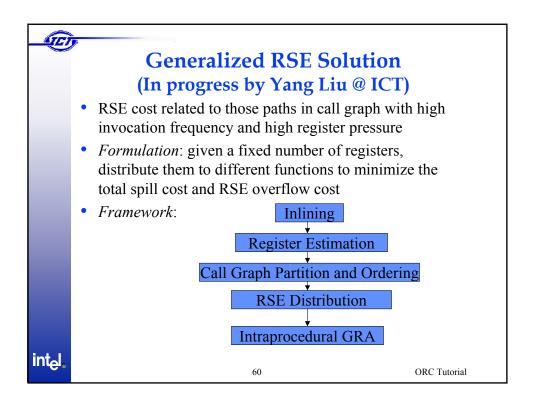

Performance Features in ORC 2.0

intel.

#### **Performance Features**

- Enable optimizations on object fields

- **对** Improved *eon* by ~40%

- Balance between RSE and register spills

- $\nearrow$  Improved *perlbmk* by > 30 %

- Memory optimizations

- Stride prefetching

- Reordering of hot/cold struct fields

- Conversions to memset/memcpy

- Tuning the cost model for function inlining

- IPA-enabled optimizations

- 7 De-virtualization, more uses of gp-rel, procedure reordering,

- Aliasing enhancements: type-based disambiguation

intel,

55 ORC Tutorial

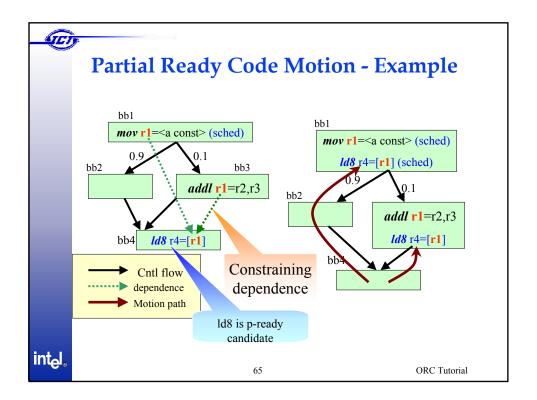

### **Performance Features (cont.)**

- Enhancements of instruction scheduling (>3% overall)

- A new, more modular implementation

- Tuning of scheduling heuristics to enable more speculation

- → P-ready code motion

- Across nested regions; branch "delay slots"; entry and exit blocks

- Efficient code expansion

- → Mul/div/rem

- → Avoid expensive loop unrolling factors

56

- → Boolean expressions

- Multiway branch synthesis

- Branch hints

intها.

#### **Performance Features (cont.)**

- Restore callee-save registers in a path sensitive manner

- Analysis of load safety to reduce the # of speculative lds

- Bundle chk's with adjacent instructions into the same cycles

- Micro-architectural features

- Padding of nop's to avoid pipeline flushes

- Taming I-cache padding and code layout

- ▼ FU-sensitive latency for scheduling

- E.g. 2 cycles for add (I)-> ld vs. 1 cycle for add (M)->

- •

- A large number of enhancements and each contributes a small gain (often < 0.5%)

intel,

57 ORC Tutorial

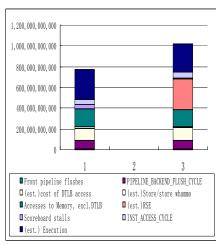

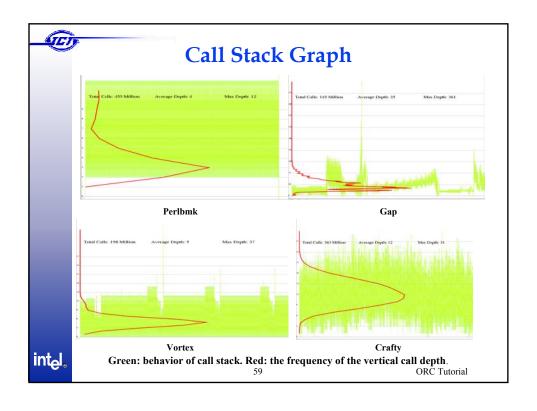

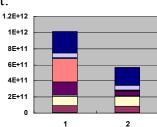

### RSE (Register Stack Engine) Problem in Perlbmk

58

- RSE Problem in perlbmk

- regmatch: self recursion and using96 registers

- Excessive stalls due to RSE

- → Average call depth: 4

- Current solution

- → Reduce register usage with spills

- Live ranges for stacked registers ordered

- Current usage of stacked registers in regmatch: 27

Performance after and before tuning

ORC Tutorial

intطا

### Optimizations for C++ Programs (by Kai Yu Chen @ ICRC)

- Some characteristics of C++ programs

- → Small member functions, structure copy, virtual function calls, abstract data class, template functions, ...

- Challenges for eon

- Insufficient inlining

- Inappropriate symbol attribute and inline heuristic

- Overhead introduced by inlining

- Excessive memory copies of structure fields

- Traditional optimizations techniques less effective to structures and fields

- Copy propagation, DCE, folding of field accesses, IVR, ...

- Delay the lowering of IR for large structures

- Flatten well organized small structures early

intel,

ORC Tutorial

### Optimizations for Structures and Fields - Examples

Remove unnecessary structure copies through copy propagation and dead code elimination

```

S2 = S1;

S3 = S2;

return S3;

```

• Remove unnecessary field accesses

62

intel,

### **Measurement for Abstract Penalty**

#### Stepanov's benchmark for measuring abstract penalty

| compiler data   | Abstraction Penalty | Total Run Time (s) |

|-----------------|---------------------|--------------------|

| Gcc (-O3, 2.96) | 1.37                | 11.29              |

| Orcc (Note #1)  | 48.10               | 63.67              |

| Orcc (Note #2)  | 28.62               | 45.97              |

| Orcc (Note #3)  | 6.82                | 7.90               |

| Orcc (Note #4)  | 4.24                | 4.76               |

| Orcc (Note #5)  | 0.77                | 0.88               |

Note: 1. ORC 1.0

- 2. Enable copy propagation and DSE for struct's

- 3. Enable inlining of template functions

- 4. Disable prefetch and enable CPROP for FP PREG inside loops

- 5. Enable indirect memory access folding and flatten struct for IVR

int<sub>e</sub>l,

63 ORC Tutorial

### Partial Ready Code Motion (by Shuxin Yang @ ICT)

- *Problem*: scheduling dependences ready on one path but not on another

- → Lost scheduling opportunities

- To schedule aggressively on hot paths by leaving compensation copies on cold, yet ready paths

- Extended from existing upward code motion

- Identify a cutting set to find the nodes collectively post-dominating the dependences not ready

- Place compensation copies on these nodes

intel.

### **Enable and Tune Function Inlining**

(by Peng Zhao @ U. of Alberta and by Ge Gan & Liping Xue @ ICT)

- Inlining: enables more optimization opportunities

- Guided by profiling feedback

- A problem: functions never invoked slipping through the cost checking and frequently getting inlined

- Taking into account: invocation frequency, sizes of caller and callee, estimated cycles in callee,

- Lowered hotness threshold to enable more inlining

- Currently ~10% improvement from IPA/inlining and expecting more

intel.

#### Memory Optimizations - Stride Prefetching (by JiaJun Wu & Xiaobing Feng @ ICT)

- $\sim 40\%$  of all cycles in SPEC CInt2000 due to data stalls (cache and DTLB)

- $\sim$ 80% of the cycles in *mcf* due to data stalls

- Prefetching can reduce data stalls

- But only stride-based prefetching has been effective and only to fp apps

- Fixed strides observed in some integer apps due to the patterns in allocation and usage of data objects

- Stride prefetching guided by profiling feedback

- → Based on the work by Y. Wu, PLDI '02

- Expecting large gains in mcf and some gains in gap and parser

intel,

67 ORC Tutorial

### Memory Opt. - Reordering of Structure Fields (by Li Chen @ICT & William Chen @ ICRC)

- Reorder hot and cold fields in objects to improve the spatial locality in cache

- Many considerations on legality and profitability

- Example: hottest loop in mcf

```

struct node {

struct node {

While (arc) {

size_t mark;

long number;

.. node->time

long time;

char *ident;

.. node->potential

cost t potential;

struct node *pred, ...

long number;

.. node->mark

char *ident;

cost t potential;

}

struct node *pred, ...

flow_t flow;

size_t mark;

flow_t flow;

long time;

}

}

```

68

أطint

### Multiway Branch Synthesis (by Lixia Liu @ ICRC)

- Utilize the multiway branch feature on IPF

- Issue more than one branch per cycle

- **对** E.g. MBB, BBB

```

(p) br B1;;

(q) br B2;;

br B3;;

(p) br B1

(q) br B2

br B3;;

```

- A separate synthesis phase after scheduling

- Branch target has to be bundle aligned

intطِ

69

ORC Tutorial

### Performance Analysis Tools and Experience

intel,

70

# **Performance Analysis Tools on IPF**

- Tools: an important part of ORC

- Automatic testing tools

- → Cycle counting tools: static and dynamic

- ▶ pfmon: to access the IA-64 PMU on Linux

- → VTune: perfromance analyzer from Intel

- Visualization tool based on daVinci

- → Hot path enumeration tool

intel.

71 ORC Tutorial

### **Automatic Testing Tools**

- Support various testing (correctness, performance, checkin, regression, etc.)

- Automatic start (crontab settings) and update the newest source from a version control system (e.g. CVS)

- Generate reports with comprehensive information.

- Customizable on many aspects:

- 7 Optimization levels: O2/O3, +profiling, +IPA, peak mode.

- Benchmarks and compilers used.

- → Compilation modes (cross/native) and running platforms.

intel,

# **Cycle Counting Tools**

- Count cycles caused by stop bits and latencies

- → Cycles due to dynamic events, e.g. cache misses, not counted.

- Count cycles of pre-selected hot functions.

- Generate reports of comparisons with history data.

- Static cycle counting

- Based on annotations in assembly code, e.g. frequency weighted cycles of each basic block.

- Need pre-generated feedback information.

- Dynamic cycle counting

- Need additional implementation to

- Insert the definitions of counters into Symtab.

- Find unused registers for instrumentation instructions.

- Frequency counted at run time.

intel,

73 ORC Tutorial

### Sample Assembly Code

74

int<sub>e</sub>l

## Sample Report Generated by the Tool

| Comparison with CVS                |           |           |            |

|------------------------------------|-----------|-----------|------------|

| THIS_TIME: 2-Jul-2002 vs. LAS      |           |           |            |

|                                    |           |           |            |

| PU_name                            | THIS TIME | LAST TIME | DELTA      |

|                                    |           |           |            |

| bzip2:generateMTFValues            | 4.554E+09 | 4.554E+09 | 0.000E+00  |

| bzip2:sendMTFValues                | 8.250E+08 | 8.250E+08 | 0.000E+00  |

| crafty:Evaluate                    | 4.564E+09 | 4.699E+09 | 1.355E+08  |

| crafty:FirstOne                    | 1.190E+09 | 1.190E+09 | 0.000E+00  |

| crafty:Attacked                    | 8.506E+08 | 8.884E+08 | 3.785E+07  |

| gap:CollectGarb                    | 2.302E+08 | 2.302E+08 | 0.000E+00  |

| gzip:longest_match                 | 7.222E+09 | 7.139E+09 | -8.334E+07 |

| gzip:deflate                       | 2.697E+09 | 2.795E+09 | 9.885E+07  |

| gzip:inflate_codes                 | 3.601E+09 | 3.601E+09 | 0.000E+00  |

|                                    |           |           |            |

| Result:                            |           |           |            |

| TOTAL:17 PASSED:17 FAILED:0        |           |           |            |

| Degraded:1 Improved:5 Unchanged:11 |           |           |            |

intel.

75 ORC Tutorial

# Performance Monitoring and pfmon

- Performance monitoring features on Itanium

- → A suite of performance monitoring registers

- → More than 150 events

- → Advanced features, such as "sampling"

- Methods of performance analysis:

- Work load characterization (Event rate monitoring and Cycle breakdown)

- Profiling (PC sampling, EAR sampling, BTB)

- pfmon: monitors runtime behavior of unmodified binaries

76

intel.

#### pfmon - Event Counting

- Count the occurrences of important events

- Example: failed data speculations

- ▶ pfmon –u –e ALAT INST CHKA LDC.ALL foo ...

- ▶ pfmon —u —e ALAT\_INST\_FAILED\_CHKA\_LDC.ALL

| orcc                         | ALAT_INST_CHKA_LDC.ALL | ALAT_INST_FAILED_CHKA_LDC.ALI | failed/all |

|------------------------------|------------------------|-------------------------------|------------|

| $\mathtt{bzip2}\overline{J}$ |                        | 325549130                     | 16.88%     |

| crafty                       | 494898879              | 56087                         | 0.01%      |

| અમાત                         | Jl. 4100283083         | 328561109                     | 8.01%      |

| gap                          | 5218362450             | 283104235                     | 5.43%      |

| gcc                          | 334475307              | 23143799                      | 6.92%      |

| gzip                         | 316462073              | 314647                        | 0.10%      |

| mcf                          | 278918345              | 3632297                       | 1.30%      |

| parser                       | 7361718884             | 755482308                     | 10.26%     |

| perlbmk                      | 2368043225             | 3676097                       | 0.16%      |

| twolf                        | 10867872791            | 637333338                     | 5.86%      |

| vortex                       | 4541508419             | 32142975                      | 0.71%      |

| vpr                          | 1385861255             | 4956940                       | 0.36%      |

intel.

7 ORC Tutorial

# pfmon - Cycle Breakdown

- Attributes a reason for every cycle spent.

- Need multiple runs to make a complete breakdown

- pfmon -k -u -e CPU\_CYCLES, EXECUTION\_CYCLE, PIPELINE\_ALL\_FLUSH\_CYCLE, DTLB\_MISSES -outfile=\$res\_file

78

• Output:

Cycle Breakdown of perlbmk

ORC Tutorial

intel,

## pfmon - Event based Sampling

- Relating performance problems back to source code.

- Example: D-cache misses causing latencies > 16 cycles

- pfmon --dear-smpl-rate=1000 -e

DATA\_EAR\_CACHE\_LAT16 --smpl-file=sample -- ls

/usr

- Output: Entry 0 PID:9239 CPU:0 STAMP:0xe468a2709334 IIP:0x200000000013750 PMD OVFL: DATA\_EAR\_CACHE\_LAT16(4)

PMD2 : 0x200000000070dd9

PMD3 : 0x00000000000011 , Latency 17

PMD17 : 0x2000000000024f30 (slot 0) valid=Y

Entry 1 PID:9239 CPU:0 STAMP:0xe468a270a75d IIP:0x200000000013580

PMD OVFL: DATA\_EAR\_CACHE\_LAT16(4)

PMD2 : 0x200000000005ace0

PMD3 : 0x00000000000014 , Latency 20 PMD17 : 0x200000000013760 (slot 0) valid=Y

79 ORC Tutorial

intel.

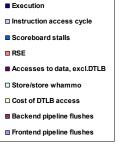

## **Intel VTune Performance Analyzer**

- Collect performance data on application and system

- → Hotspots, critical functions

- Processor events, e.g. cache misses

- Various collectors with display in graph or table

- Counter monitor

- Sampling

- Call graph

- Use collected info to identify performance bottlenecks

- Experience in finding the deficiencies in compiler

- → Cannot modify apps' source code

- Performance bottlenecks may be legitimate

- → Still need much work to map to an root cause

intel,

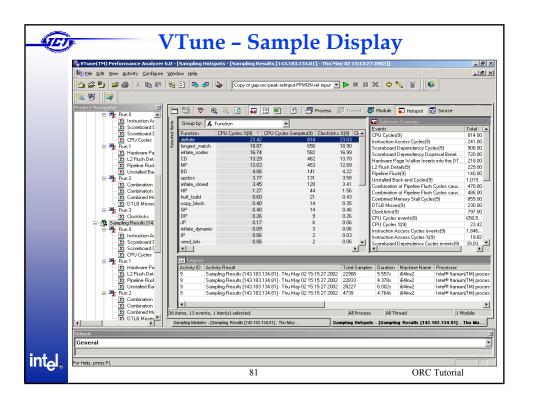

#### **Visualization Tool**

- Based on daVinci: an X-Window visualization tool from b-novative, a spin-off of University of Bremen.

- ORC can communicate with daVinci and support interactive examination of graph-based data structures.

- Various internal data structures visualized in ORC:

- Global and regional CFG, region tree

- Regional and local (basic block) dependence DAG

- Predicate partition graph

- CFG visualization tool on assembly code

82

intel.

# Hot Path Enumeration Tool - hpe.pl

- Motivation:

- Analyzing assembly code of large PUs is tedious.

- 7 Focusing on hot paths only is more effective.

- Uses of the tool:

- → Find performance hot spots / defects.

- Comparison between different compilers.

- Comparison between different versions of same compiler.

intel.

83 ORC Tutorial

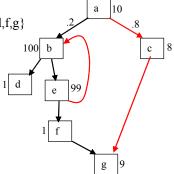

## Hot Path Enumeration - an Example

- Example:

- **▼** Two loops:

- $\nearrow$  Loop2={b,e}

- → Hot paths

- In loop1:

- 7 path = a, d freq=1

- 7 path = a, f, g freq=1

- 7 path = a, c, g freq=8

- In loop2:

- 7 path = b, e freq=99

84

intel,

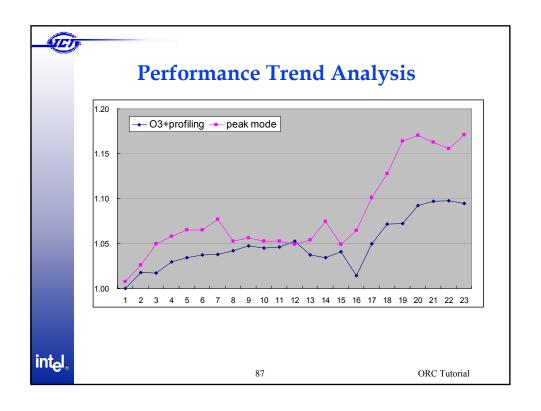

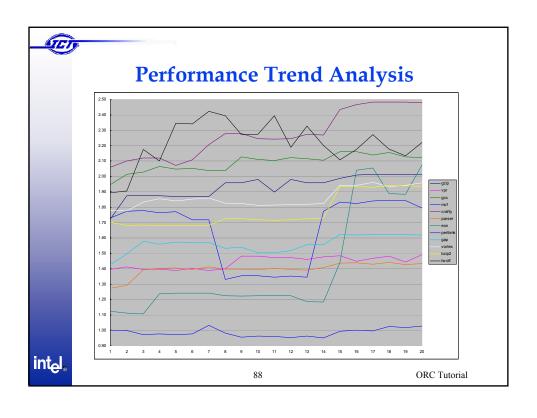

# **Driving the Performance of ORC**

- Avoid performance regression

- Checkin testing and criteria

- 7 Fast investigation of performance degradations.

- Identify new opportunities through continuous performance analysis

- Inspection of assembly code for hot paths in hot functions

- Comparisons between different compilers

- Understanding the performance impact of various enhancements.

intel,

85 ORC Tutorial

#### **Investigation of Degradations**

- Some methods

- → Repeat the testing to filter out noises.

- → Check cycle counts of pre-selected hot functions.

- → Check the corresponding assembly code.

- Make hypothesis on causes, conduct experiments, and prove or disprove the hypothesis.

- → Use pfmon to find out the effects of dynamic events.

86

**7** ...

intel.

# **Summary: What We Have Learned**

- Performance analysis is the base of gaining performance.

- Two steps for understanding and tuning performance

- Workload characterization

- → Profiling

- Tools are important

- Reduce the time and tedious manual work needed.

- Help understand various aspects of performance

- Methodology also important

- Progress in the right direction

- → Avoid regression

intطِ。

89 ORC Tutorial

Demo

intel.

90

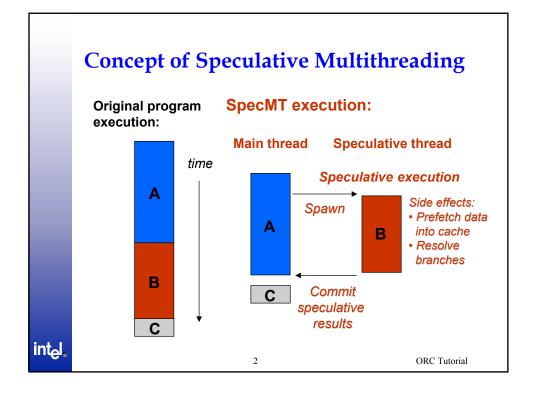

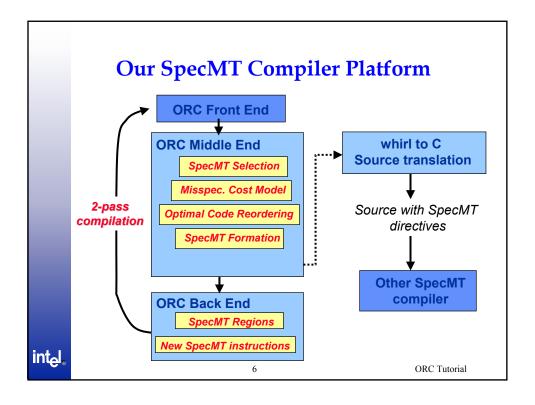

# Use of ORC in Compiler Research for Speculative Multithreading (SpecMT)

Tin-Fook Ngai @ MRL Zhaohui Du, Tao Huang\*, William Chen @ ICRC Saisanthosh Balakrishnan @ U. Wisconsin

intطِ。

## Hardware Supports for SpecMT

- Special SpecMT instructions

- **对** Fork, kill, etc.

- Speculative execution

- Buffering of speculative results

- → No exception on speculative execution

- Dependence checking

- 7 Check for register/memory RAW dependence violation

- Recovery upon misspeculation

- 7 Trash all speculative results and re-execute, or

- Commit correct results and re-execute only misspeculated instructions

intel,

ORC Tutorial

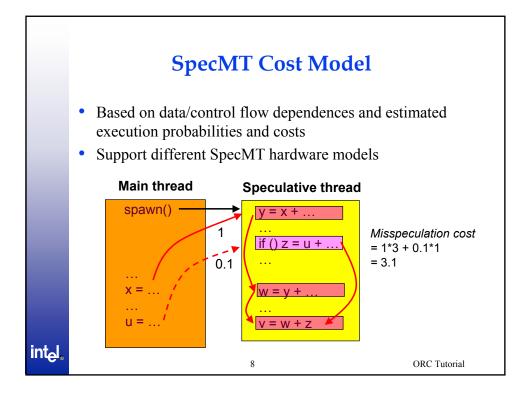

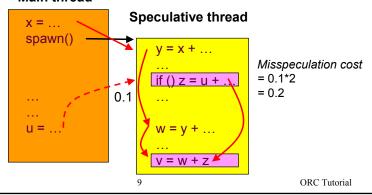

#### **SpecMT Compiler Research Issues**

- How to identify and expose every good SpecMT opportunities in a program?

- → Good program coverage by SpecMT is essential

- How to analyze and manage thread-level speculation?

- Misspeculation cost modeling

- Need new probabilistic dependence, alias and value analyses

- How to optimize SpecMT code?

- 7 To reduce misspeculation

- How to best tailor for different forms of hardware supports?

intel.

# SpecMT Compiler Research at Intel/PSL

- To identify opportunistic speculative threads

- → When and which thread to spawn

- → Initial focus on loops

- To restructure/transform programs

- More SpecMT opportunities, less misspeculation

- To minimize misspeculation penalty

- Precompute or predict critical data value before spawning

- → Schedule inter-thread dependent instructions far apart

int<sub>e</sub>l,

## **Optimal Code Reordering**

- Reorder code before SpecMT spawn point to minimize misspeculation cost

- Reduce critical path to spawn SpecMT threads early

#### Main thread

intط,

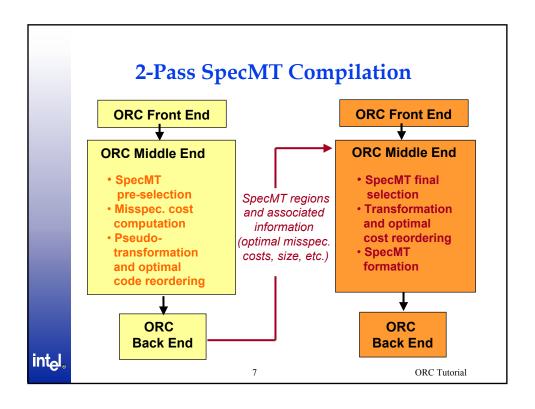

# Changes and Enhancements to ORC (1)

#### **ORC Middle End**

- A new SpecMT phase in mainopt

- Right after SSA construction, IVR, copy propagation and first DCE

- Build internal dependence graph with estimated coderep sizes and profile-feedback edge probabilities

- Perform code reordering inside the loop body

- Tackling the non-overlapped live range requirement in ORC SSA

- Handling of motion of partial conditional statements

- → Insert SpecMT directives as intrinsic calls

10

intel,

#### Changes and Enhancements to ORC (2)

#### **ORC Middle End**

- Unique loop id assignment

- 7 For loop matching in the 2-pass compilation

- Propagate preopt loop id to mainopt and reassign loop id after LNO

- IPA summary of function size information

- LNO: Selective loop unrolling

- → Including outer loop unrolling

intel,

11 ORC Tutorial

#### Changes and Enhancements to ORC (3)

#### **ORC Backend**

- Introduce and schedule new SpecMT instructions

- Have similar semantics to existing chk instructions but executed on B-unit

- Minor change to the existing machine model

- Translate SpecMT intrinsic calls from Whirl to SpecMT instructions in CGIR

- Form SpecMT regions

- Both for the SpecMT thread body and for the preparation code before the fork instruction

- Mark SpecMT regions to be NO\_OPTMIZATION\_ACROSS\_REGION\_BOUNDARIES

12

intel,

### Changes and Enhancements to ORC (4)

#### **ORC** Backend

- CFO and EBO

- → Before Region Formation, disable the first CFO stage and limit EBO within single basic block

- Make CFO and EBO being aware of regions with NO\_OPTMIZATION\_ACROSS\_REGION\_BOUNDARIES and honor the no-optimization attribute

- Check blocks for region memberships

intel.

13 ORC Tutorial

# Changes and Enhancements to ORC (5)

#### Whirl2C

- Many fixes to allow source translation of low-level whirl emitted from main-opt

- Skip machine-dependent whirl lowering after the second DCE

14

intel.

# Our Experience with ORC

- A solid, full featured compiler to start with

- Good and handy supports:

- 7 Rich IR and supports: whirl, SSA, regions in CGIR

- Profile feedback and IPA

- → Flexible machine model

- → Whirl2c

- Major problems w.r.t. our work

- 7 Code reordering is complicate with ORC SSA due to its nonoverlapped live range requirement (and we solved part of it)

- → Limited outer/while-loop optimizations

- Current CG phases (including scheduler) do not fully honor region attributes

- CFO and EBO in CG are not region-based but we made it region-aware (w.r.t. one key attribute)

intel,

# **Compiler Research on IA-64**

Haibo(Jason) Lin

Institute of HPC

Dept. of CS&T, Tsinghua University

# Agenda

- ❖ Research on ILP

- ➤ Performance of SWP

- ➤ Loops Fail to SWP (SWP Failure)

- ➤ Solutions to SWP Failure

- Research on TLP

- ➤ OpenMP Research

- ➤ Project Overview

- > Some Experiments and Results

# ILP-Performance of SWP

❖ A speedup of 10% (SPEC fp2000)

❖ A speedup of 48% (NPB 2.3-serial)

2002-11-6 Dept. of CS&T, Tsinghua University

#### **ILP-SWP Failure**

- Statistics

- > 4.7% in SPEC fp2000 (3,000 loops)

- ➤ 6.8% in NPB (400 loops)

- ❖ Cause of SWP failure

- ➤ Loop too big

- 37% in SPECfp, 20% in NPB-serial

- ➤ Non-rotating register not enough (general register)

- 63% in SPECfp, 80% in NPB-serial

- Base update TN accounts for non-rotating register pressure // ld4 r1=[r2], 4

#### **ILP-Solutions to SWP Failure(RSU)**

- ❖ Solution 1-Register Sensitive Unrolling(RSU)

- ➤ Why unrolling?

- Increasing the number of instructions visible to compiler

- Enabling factional MII(Minimum Initiation Interval)

- 5 additions / 2 adders → MII= 5/2 = 3 cycles

- Unroll 2 times → MII= \[ 10/2 \]=5 cycles

- Increasing register requirements

- ➤ Limiting unrolling factor(K)

- Recalculating K According to register requirements

- Increased SWP-ed loops

2002-11-6

May lead to performance decline due to poor schedule caused by improper unrolling factor

Dept. of CS&T, Tsinghua University

#### **ILP-Solutions to SWP Failure(SRA)**

- Solution 2-Stacked Register Allocation(SRA)

- Currently SWP can only use static register as nonrotating register

Static

Stacked rotating

Stacked callee Stacked caller

Allocate stacked register to TNs which need Nonrotating register

Static

Stacked rotating

Stacked Non-rotating Stacked callee

Stacked caller

2002-11-6

Dept. of CS&T, Tsinghua University

#### **ILP-Conclusion**

- SWP failure is mainly caused by insufficient non-rotating registers

- RSU & SRA both provide doable solutions to SWP failure

- RSU may lead to performance decline due to improper unrolling factor, and sometimes can not solve SWP failure problem

- SRA performs better than RSU by allocating general register more efficiently

2002-11-6

Dept. of CS&T, Tsinghua University

## **TLP-Project Overview**

- ORC based OpenMP compiler

- **>** Goal

- Develop an compiler that produces multithreaded programs that can explore intra-die(Hyper threading) and inter-dies (SMP) TLP

- Motivation

- Study characteristics of OpenMP itself: how to build up a high performance implementation

- Find optimizing opportunity for OpenMP implementation and codes written in OpenMP: find out suitable program forms to carry on source-level optimization

- A testbed for parallelization: compiling for the SMP clusters

#### **TLP-Project Plan**

- Framework building

- ➤ A base module support on selected Fortran 77 OpenMP directives

- ➤ Works relatively well

- Extending to OpenMP Fortran API v1.0

- Extending to OpenMP Fortran API v2.0

- Fortran(v2.0)/C frontend building

- Debugging phase for stability and performance

- > Regression test and performance tuning

2002-11-6

Dept. of CS&T, Tsinghua University

## **TLP-Project Progress**

- OpenMP tranform module

- ➤ Have the same function as original SGI module, except for workshare/threadprivate handling(done)

- ❖ Fortran90 FE

- > In working. Tuning for final release

- ❖ C FE

- ➤ The Lex/Yacc part has been done

- > The WHIRL transformation module is in working

- ❖ TO DO

- Profiling support for OpenMP performance tuning

- Source-level OpenMP parallelization and optimizing techniques

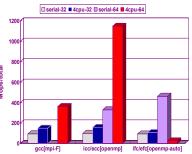

# **TLP-Experiments and Results**

#### ❖ An example-BT.W

Platform (Fig. of the right column)

xx-32: 4 \* Xeon 700MHz, 1G Mem, 1.24G network, Linux 2.4.7-10smp

xx-64: 4 \* Itanium2 900MHz, 4G Mem, 1000M network, Linux 2.4.9-18smp

12

2002-11-6

Dept. of CS&T, Tsinghua University

## **TLP-Experiments and Results**

#### Conclusion

- ➤ Compiler optimization is critical for IA-64 based platform

- ➤ Parallel compiler is still constrained by its own ability

- ➤ The performance of Itanium2 SMP + ecc + OpenMP could be very good

- ➤ With the best optimizing effort by both programmer and compiler, the performance of Itanium2 SMP is 6~10 fold over that of Xeon SMP

- > The performance per MHz (floating point) of Itanium2 SMP is 4.5~7.5 fold over that of Xeon SMP

2002-11-6

# The End

#### Thanks!

For more information, please mail to:

linhaibo99@mails.tsinghua.edu.cn(ILP)

chenyj99@mails.tsinghua.edu.cn(TLP)

2002-11-6

13

#### Research Activities in Academia

- University groups using ORC/Open64 as reported in PACT02 tutorial and in the past

- <sup>7</sup> U. Del, U. Minn, U. Ghent, Georgia Tech, U. Maryland,

- Rice U., TsingHua U., Peking U., Alberta U., CAS, U. Houston, Princeton

- More universities and research groups:

- MIT, Prof. Saman Amarasinghe

- · Predication and scheduling

- Zawrence Berkeley Lab

- Global address space language (e.g. upc)

- Adjoint Compiler Technology & Standard project

- 7 Fortran 95 Automatic Differentiation Tool

93 ORC Tutorial

# Known Publications Based on ORC/Open64

- Speculative Register Promotion Using Advanced Load Address Table (ALAT)

To appear in the CGO-1 Conference, '03.

- EPIC Instruction Scheduling Based on Optimal Approaches

1st Annual Workshop on EPIC Architectures and Compiler Technology

- SSA Predicated Execution Code Scheduling on SSA form for Itanium

- Maximizing Pipelined Function Units Usage for Minimum Power Software Pipelining 20-th Int'l Conf. On Computer Design, 02

- A near-optimal instruction scheduler for a tightly constrained variable instruction set embedded processor

- 1st Int'l Conf. On Compilers, Architectures, and Synthesis for Embedded Systems, 02

- Engineering a C compiler for the Cognigine cgn1600 Network Processor Network Processor Conferences, 2002

- Effective Compilation Support for Variable Instruction Set Architecture Int'l Conf. On Parallel Architecture and Compilation Techniques, 02

- Reuse Distance-Based Cache Hints Selection 8th Int'l Euro-Par Conf., 02

- SCALEA: A Performance Analysis Tool for Distribution and Parallel Programs 8th Int'l Euro-Par Conf., 02

- More ...

intط

94

## Checkins and Merges on the Plan

- ORC2.0 early Jan 03 (ICT/ICRC-Intel/PSL-Intel)

- ORC2.0 merge into Open64 soon afterward (U. of Delaware)

- OpenMP support for 2.96 gcc, orcf90 (TsingHua U.)

- → V1.0 early next year

- → V2.0 soon afterward

- U. of Minnesota merge early 03 discussed

- Other merges waiting?

intطِ

95

ORC Tutorial

# **Upcoming User Forum**

- On the plan

- During CGO Conference

- → Late March, '03 in San Francisco

- → Agenda still open

- → Would like to get suggestions

intel.

96

#### **Future Plan**

- Continued activities at Intel

- Programming Systems Lab

- Speculative multithread compilation and microarchitecture

- Streaming data compilation

- → Barcelona Lab/UPC

- Multithread compilation

- Continued activity at Chinese Academy of Sciences

- → Streaming data and network processor compilation

intel.

97 ORC Tutorial

### **Contributions and Acknowledgements**

- Institute of Computing Technology, Chinese Academy of Sciences

- Programming Systems Lab, Intel Labs

- Intel China Research Center, Intel Labs

- Pro64 developers

- Many ORC/Open64 users

intها.